Comparing Lock-Step, redundant execution & Split-Lock - Embedded blog - Arm Community blogs - Arm Community

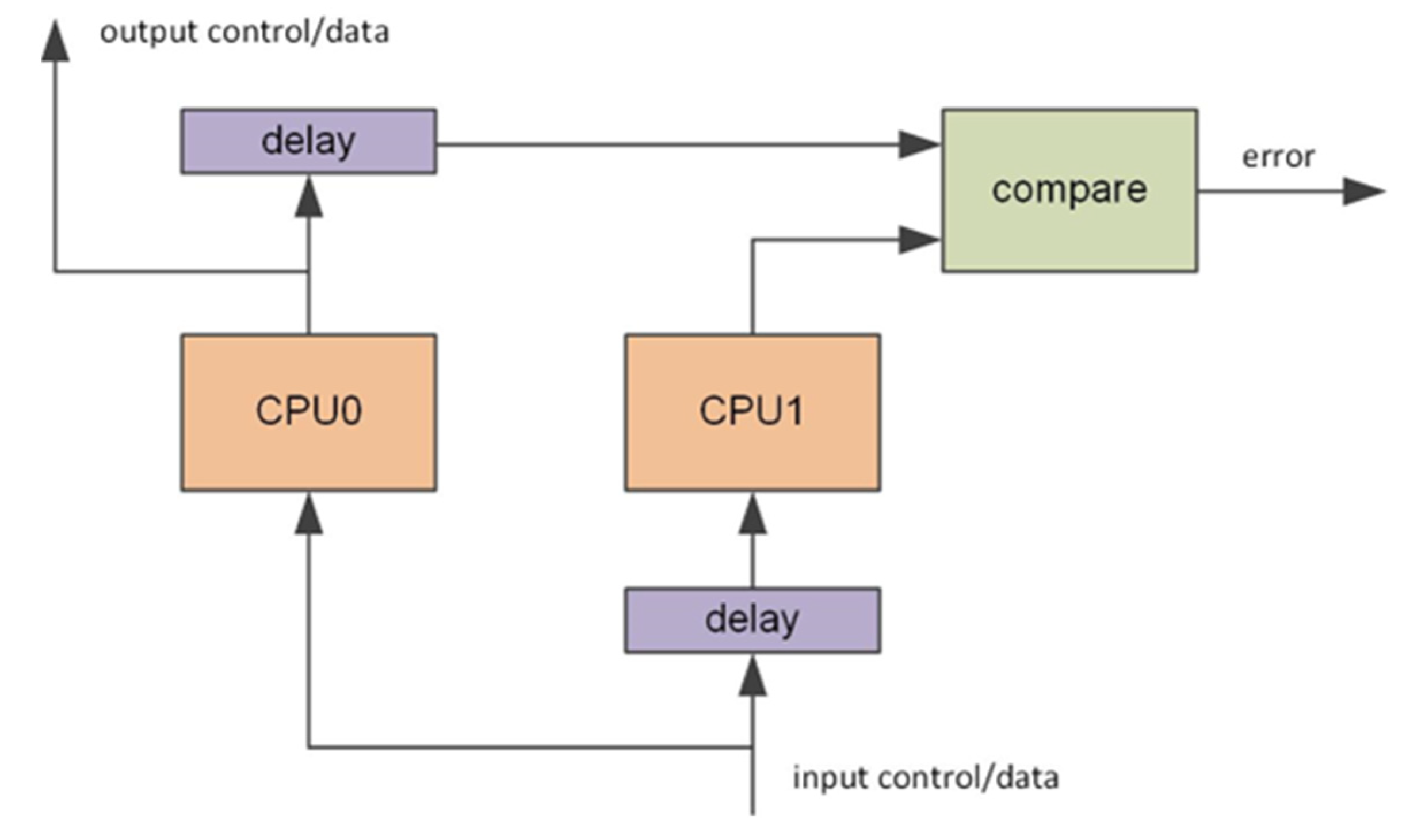

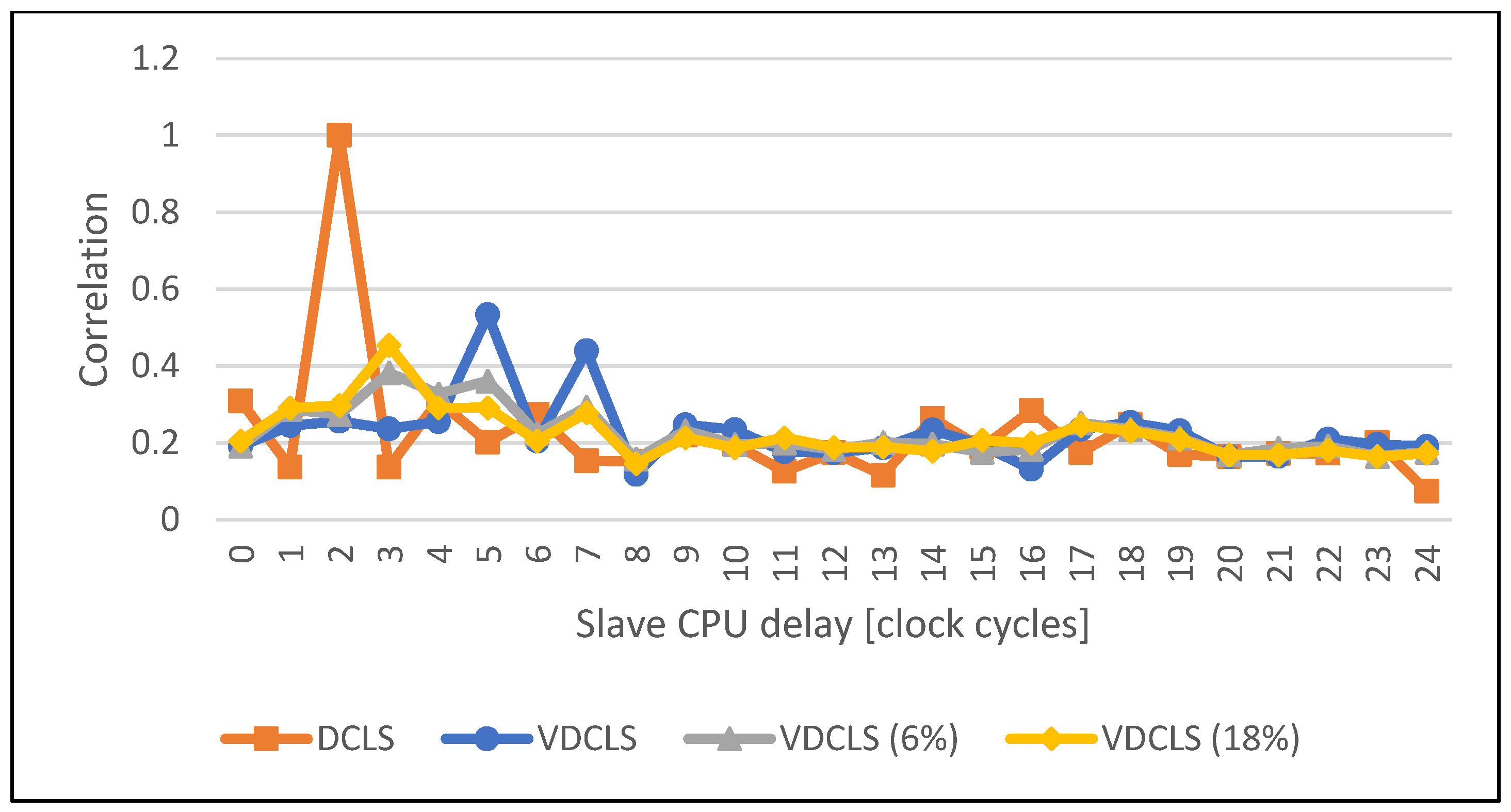

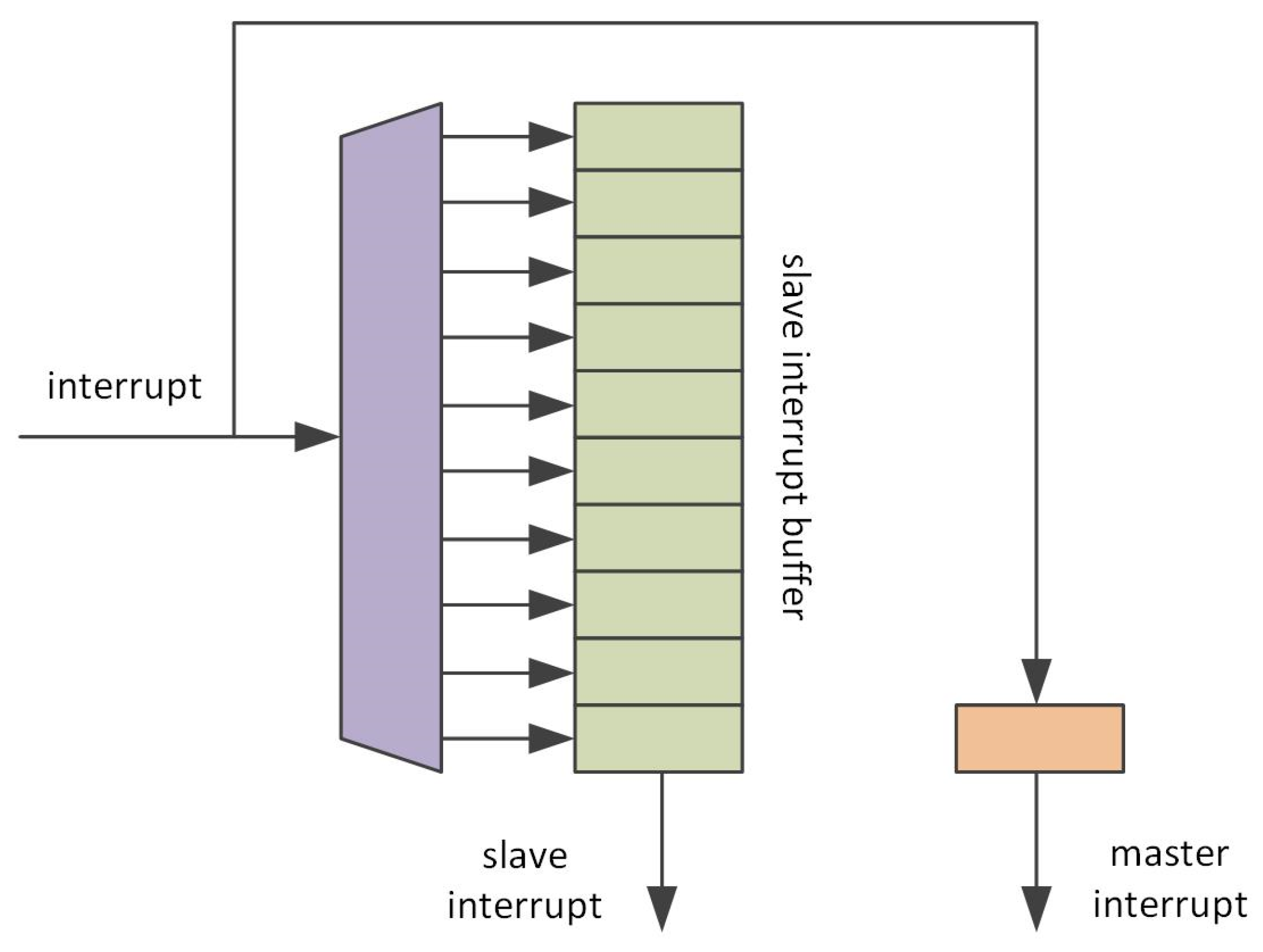

Electronics | Free Full-Text | Variable Delayed Dual-Core Lockstep (VDCLS) Processor for Safety and Security Applications

A Triple Core Lock-Step (TCLS) ARM® Cortex®-R5 Processor for Safety-Critical and Ultra-Reliable Applications | Semantic Scholar

Lone Star Gazette (Dublin, Tex.), Vol. 1, No. 20, Ed. 1 Saturday, June 17, 2000 - The Portal to Texas History

EEG Complexity Increases in Lockstep with Stimulus Consumption - Sapien Labs | Neuroscience | Human Brain Diversity Project

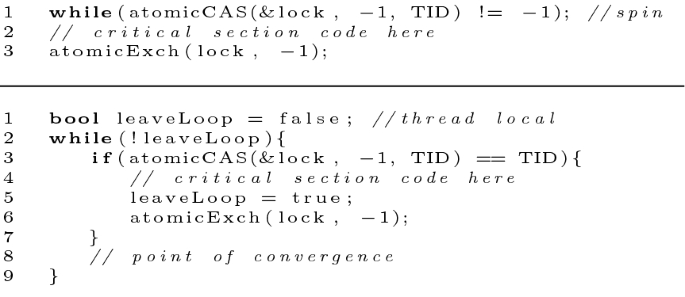

New Techniques for Improving the Performance of the Lockstep Architecture for SEEs Mitigation in FPGA Embedded Processors – topic of research paper in Computer and information sciences. Download scholarly article PDF and

Canada, U.S. in Lockstep for Support to Ukraine, NATO > U.S. Department of Defense > Defense Department News

Figure 3 from A Triple Core Lock-Step (TCLS) ARM® Cortex®-R5 Processor for Safety-Critical and Ultra-Reliable Applications | Semantic Scholar

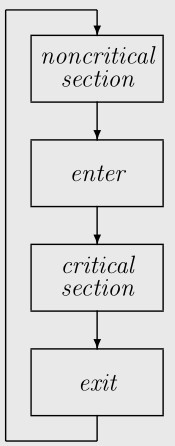

Dual-Core Lockstep enhanced with redundant multithread support and control-flow error detection - ScienceDirect

Electronics | Free Full-Text | Variable Delayed Dual-Core Lockstep (VDCLS) Processor for Safety and Security Applications