KR100969864B1 - Cml type d flip-flop and frequency divide-by-odd number using the same - Google Patents

Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool

OAK 국가리포지터리 - OA 학술지 - Transactions on Electrical and Electronic Materials - High-speed CMOS Frequency Divider with Inductive Peaking Technique

Electronics | Free Full-Text | 40 GHz VCO and Frequency Divider in 28 nm FD-SOI CMOS Technology for Automotive Radar Sensors

A FULLY DIFFERENTIAL HIGH-SPEED LOW VOLTAGE DOUBLE-EDGE TRIGGERED FLIP-FLOP ( DETFF ) | Semantic Scholar

An improved current mode logic latch for high‐speed applications - Kumawat - 2020 - International Journal of Communication Systems - Wiley Online Library

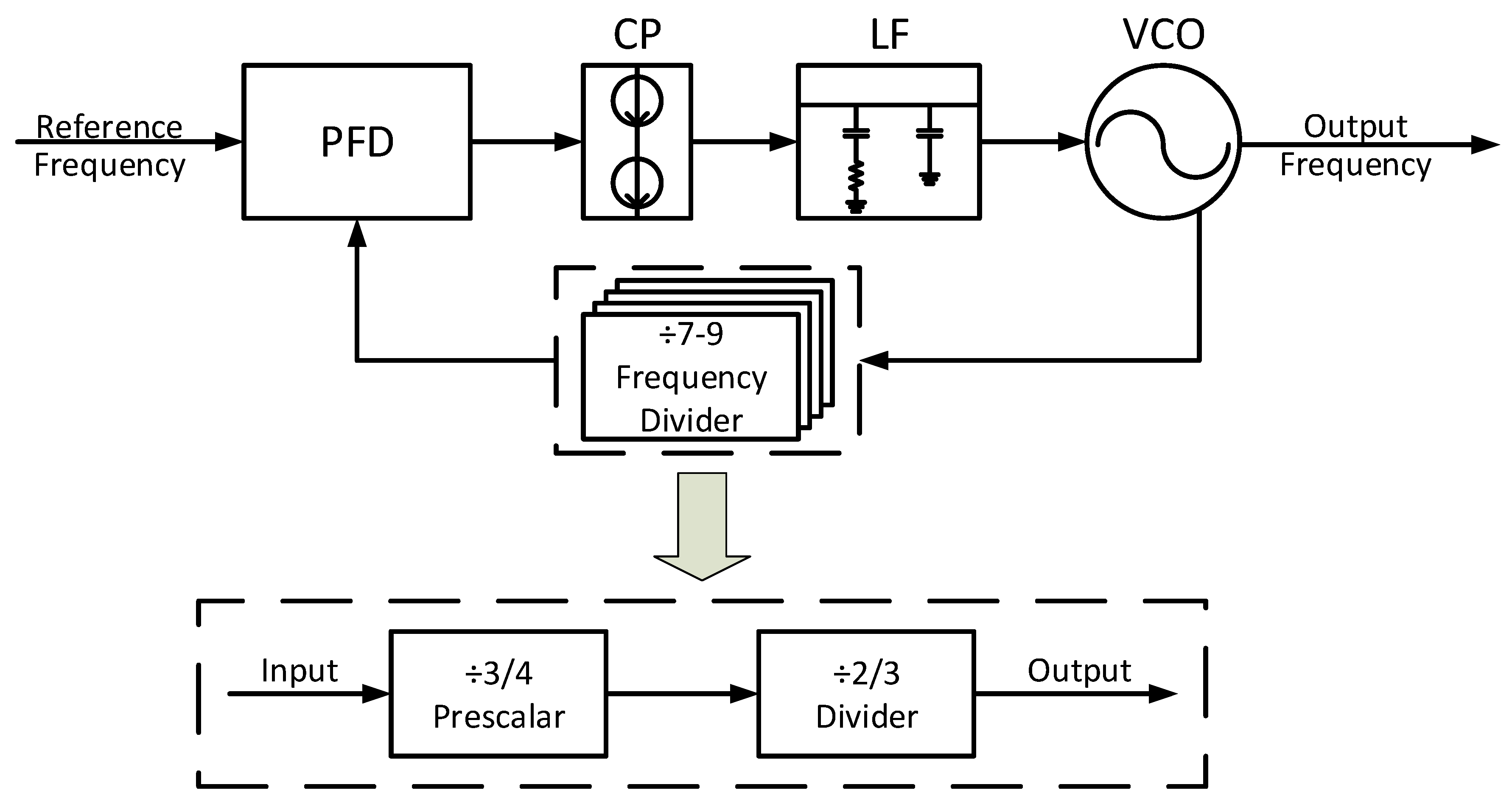

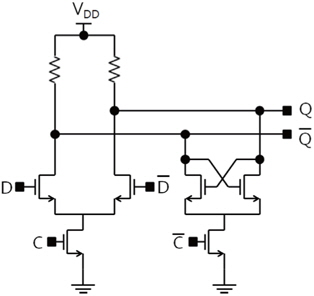

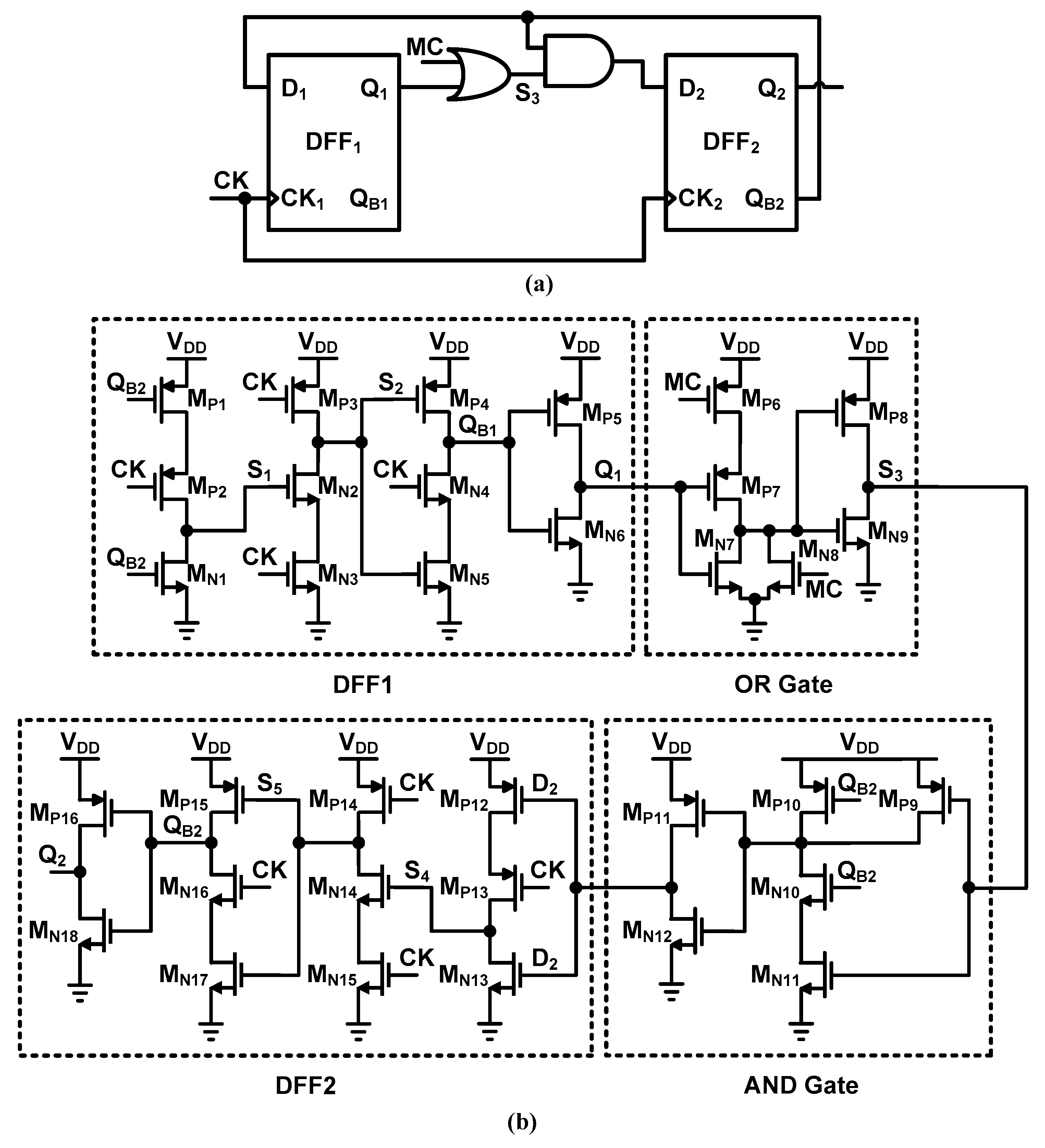

Electronics | Free Full-Text | High-Speed Wide-Range True-Single-Phase-Clock CMOS Dual Modulus Prescaler