KR100969864B1 - Cml type d flip-flop and frequency divide-by-odd number using the same - Google Patents

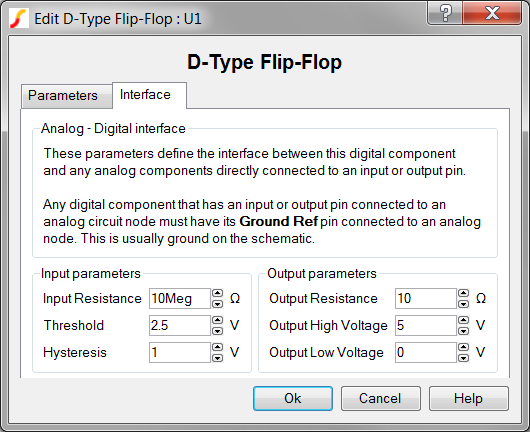

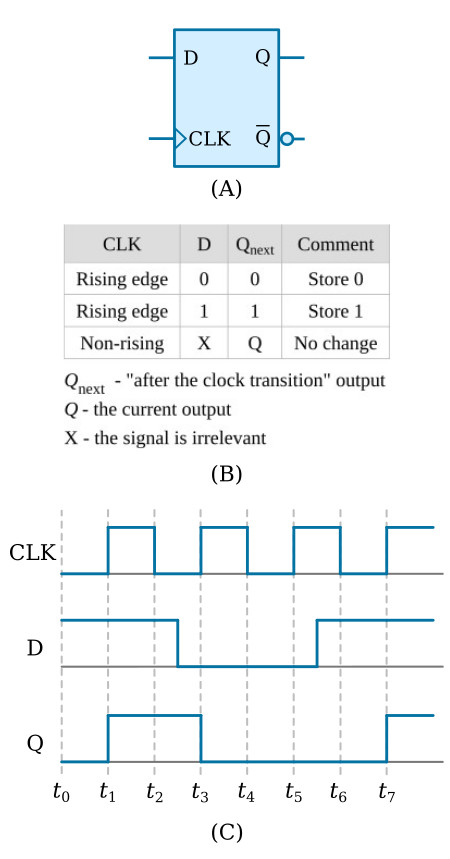

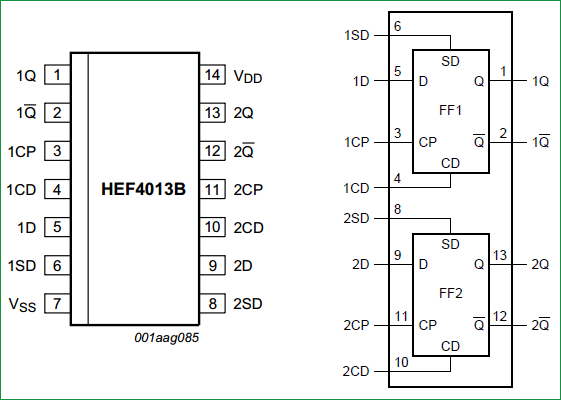

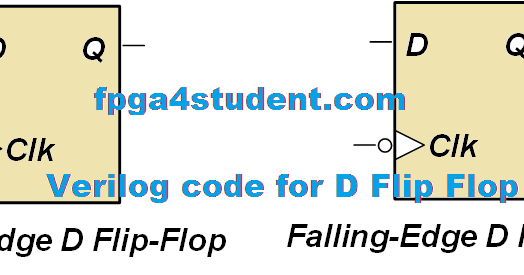

Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool

KR100969864B1 - Cml type d flip-flop and frequency divide-by-odd number using the same - Google Patents

Design of Low Voltage D-Flip Flop Using MOS Current Mode Logic (MCML) For High Frequency Applications with EDA Tool

a) Latch sensitivity function for CML latch (solid) and SenseAmp latch... | Download Scientific Diagram

Comparison of (a) CML-sampling latch and (b) SenseAmp-style latch for... | Download Scientific Diagram